當前位置: CompoTech China > 策略&營運(舊版) >

Achronix Semiconductor董事長兼首席執行官Robert Blake

在2010年,Intel與Achronix共同宣布達成22nm FPGA工藝代工協議,讓這家之前鮮有人知的企業,一下吸引了業界的目光,其最高頻率1.5GHz、陣列密度為10萬到70萬LUT 的Speedster22i FPGA已于2013年開始量產出貨。

現在,距離2010年已經過去了4個摩爾定律周期,FPGA產業格局已經發生了很大改變,Intel通過高價收購Altera表達了處理器制造商對FPGA產品的渴求(其實Intel在2009年就已經對Altera表現出了興趣),明確了FPGA在未來計算架構中的重要地位。Achronix則更進步地的認為,現有的傳統FPGA不足以覆蓋未來的市場需求,特別是未來對計算性能的巨大需求。

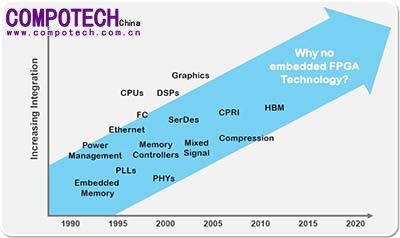

在半導體芯片設計制造中,SoC(System on Chip)這一趨勢從未改變,透過SoC技術,芯片設計人員正在盡可能多地將將許多硬件單元整合在一起。PLL、嵌入式內存單元、電源管理、內存控制器、混合信號控制、DSP、圖形核心等等,今天的SoC芯片內部正在變得日益復雜,那么為什么不將FPGA也整合到芯片中去呢?

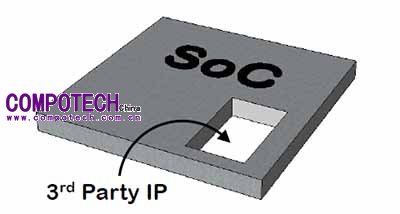

Achronix公司給出了肯定的答案:embedded FPGA技術(簡稱eFPGA)。這讓這家公司的商業模式變得更加清晰,他們將像ARM那樣提供IP授權,讓客戶將他們的eFPGA放到自己的SoC當中,而不是像傳統FPGA供應商那樣直接提供FPGA芯片及系統,畢竟相比那些久經考驗的FPGA供應商,他們還弱小很多。

Achronix eFPGA技術

近日,Achronix 宣布:推出可集成至客戶系統級芯片(SoC)中的Speedcore™ 嵌入式FPGA(embedded FPGA ,eFPGA)知識產權(IP)產品,并即刻開始向客戶供貨。Speedcore是專為計算和網絡加速應用而設計,它和Achronix的Speedster22i FPGA基于相同的高性能架構,而后者已于2013年開始量產出貨。

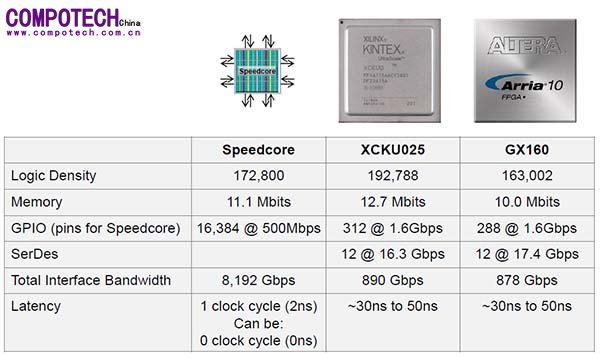

Speedcore嵌入式FPGA將吞吐量性能提高了10倍,功耗降低了50%,成本降低了90%

Achronix eFPGA與現有主流產品的性能比較

利用Speedcore IP產品,客戶可以針對其應用來定制最佳的芯片面積、功耗和資源配置。客戶可以定義查找表(LUT)、嵌入式存儲器以及DSP的數量。此外,客戶可以定義Speedcore的寬高比、輸入輸出(IO)端口的連接,還可以在功耗和性能之間進行權衡。Achronix提供了Speedcore IP產品的GDS II文件,客戶可直接將其集成至自己的SoC中;Achronix還提供了其ACE設計工具的一個定制化的全功能版本,客戶可用來對Speedcore eFPGA的功能進行設計、驗證和編程。

“多年以來,不同的公司都一直在談論eFPGA產品,但Achronix的Speedcore是首款向客戶出貨的eFPGA IP產品,它是游戲規則的改變者,”Achronix Semiconductor董事長兼首席執行官Robert Blake表示。“Achronix曾是第一家提供帶有嵌入式系統級別IP的高密度FPGA的供應商。我們正在使用相同的、經過驗證的技術向客戶提供我們的eFPGA產品,這些客戶都希望將ASIC設計的各種高效能和eFPGA可編程硬件加速器的靈活性結合在同一款芯片中。”

Speedcore現在已經可以提供基于臺積電(TSMC)的16納米FinFET Plus(16FF+)工藝的Speedcore IP產品,并且正在開發基于臺積電的7納米工藝的IP。客戶可以透過Achronix的ACE設計工具立即編譯其設計,以在性能、資源使用和編譯時間等方面評估Speedcore IP。此外,Achronix擁有關于Speedcore功能和ASIC集成流程方面的完整文檔。希望了解Speedcore芯片面積和功耗等信息的客戶可以聯系Achronix,以獲取其特定Speedcore尺寸及工藝的詳細資料。

Robert Blake特別指出:除了性能、功耗、及成本上的優勢,Achronix現已全面提供Speedcore IP產品,并且已經有客戶制造出實際產品,而競爭對手的SoC FPGA最起碼要等上3年才能見到。

無論對Achronix還是FPGA行業來說,eFPGA這個新鮮事物都是非比尋常的一步,這將為FPGA公司帶來新的市場機會,現有的50億美的市場規模很可能會翻倍,那么屆時鮮有FPGA市場的格局很可能會發生巨變。

附錄:

Speedcore優勢包括:

• 更低的功耗:

o Speedcore以內部連線方式直接連接至SoC,從而省去了在外置獨立FPGA中可見的大型可編程輸入輸出緩沖(IO buffer)。可編程輸入輸出電路的功耗占據了獨立FPGA總功耗的一半。

o Speedcore的芯片面積可以根據客戶最終應用的需求而定制。

o 為了更低的功耗,客戶可以調整工藝技術來實現性能的平衡。

Speedcore優勢包括:

• 更低的功耗:

o Speedcore以內部連線方式直接連接至SoC,從而省去了在外置獨立FPGA中可見的大型可編程輸入輸出緩沖(IO buffer)。可編程輸入輸出電路的功耗占據了獨立FPGA總功耗的一半。

o Speedcore的芯片面積可以根據客戶最終應用的需求而定制。

o 為了更低的功耗,客戶可以調整工藝技術來實現性能的平衡。

• 更高的接口性能:

o 相比獨立的FPGA芯片接口,Speedcore IP 的接口延遲更低、性能更高。Speedcore通過一個超寬的并行接口連接至ASIC,而獨立的FPGA通常通過一個高延遲的串行器/解串器(SerDes)架構進行連接。

o 相比獨立的FPGA芯片接口,Speedcore IP 的接口延遲更低、性能更高。Speedcore通過一個超寬的并行接口連接至ASIC,而獨立的FPGA通常通過一個高延遲的串行器/解串器(SerDes)架構進行連接。

• 更低的系統成本:

o 因為省去了可編程輸入輸出緩沖(IO buffer)架構,Speedcore的芯片面積比獨立的FPGA小得多。

o 由于FPGA擁有較高的引腳數,為了支持這些引腳的扇出,PCB需要較多的層數,采用Speedcore IP可以避免這個問題。另外,Speedcore省去了對獨立FPGA周邊所有支持性元器件的需求,這些元器件包括電源調節器、時鐘發生器、電平位移器、無源元件和FPGA冷卻器件。

o 因為省去了可編程輸入輸出緩沖(IO buffer)架構,Speedcore的芯片面積比獨立的FPGA小得多。

o 由于FPGA擁有較高的引腳數,為了支持這些引腳的扇出,PCB需要較多的層數,采用Speedcore IP可以避免這個問題。另外,Speedcore省去了對獨立FPGA周邊所有支持性元器件的需求,這些元器件包括電源調節器、時鐘發生器、電平位移器、無源元件和FPGA冷卻器件。

• 更高的系統可靠性和良品率:

o 將FPGA的功能集成至一片ASIC中,可消除在印制電路板上放置一顆獨立的FPGA所造成的可靠性和良率損失。

o 將FPGA的功能集成至一片ASIC中,可消除在印制電路板上放置一顆獨立的FPGA所造成的可靠性和良率損失。