當前位置: CompoTech China > 關鍵技術和應用 >

新一代即插即用的數字D類音頻放大器的性能遠遠優于傳統的模擬D類放大器。更重要的是,數字D類放大器還具有低功耗、低復雜性、低噪聲和低成本的優勢。

電子產品生產商通常使用不帶濾波器的高效率模擬D類放大器來滿足手機、平板電腦、家用監控和智能音箱中便攜揚聲器的功率需求。這些D類放大器可直接連接到電池,以盡可能地降低損耗并減少組件數量。這些放大器還可實現大于80dB的電源抑制比,這對于避免GSM通訊的217Hz干擾來說非常重要。

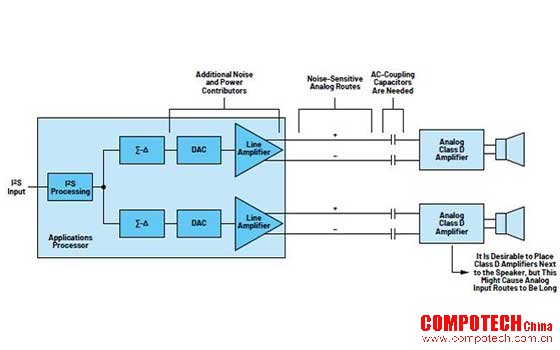

模擬D類放大器一般需要在處理器側使用DAC和線路驅動放大器(圖1),這會增加芯片成本和功耗,并導致揚聲器的輸出噪聲。這種D類放大器還要求良好的電路板布局設計,以避免信號耦合到模擬電路而導致性能下降。

圖1.使用模擬D類放大器的常規系統。處理器側的DAC和線路驅動放大器會增加成本、功耗和揚聲器輸出噪聲。

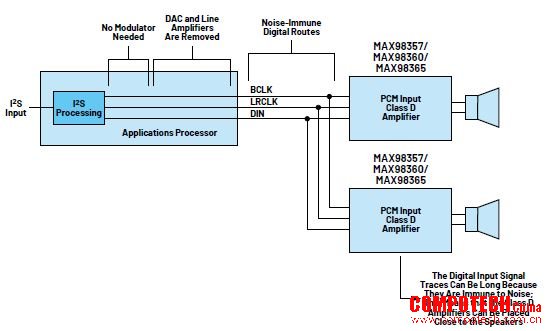

數字D類音頻放大器則不需要特殊的電路板布局設計。這些單通道D類放大器可以放置在電路板上的較遠位置,以最大限度地減少電池和揚聲器負載之間的走線。這些放大器不需要模擬D類放大器所必需的DAC和線路驅動放大器,可以降低尺寸和成本,設計更為簡單。

簡化系統設計

大多數數字放大器接收脈沖編碼調制(PCM)或I2S數據輸入時,需要三根連接線:BCLK、LRCLK和DIN。PCM格式的輸入不需要在處理器側使用調制器或對數據進行上采樣(圖2)。較早的PCM輸入的放大器需要干凈的主時鐘( MCLK)以生成無抖動的采樣時鐘,而較新的PCM輸入的放大器,如MAX98357、MAX98360和MAX98365等,則不再需要MCLK輸入,因此引腳數、功耗和電路復雜度都大大降低。

圖2.PCM輸入的數字D類放大器系統只需要使用三根連接線,而且處理器側不需要調制器或對數據進行上采樣。

較早的數字放大器提供可調的采樣速率和/或位深度,因此在某些情況下需要對放大器進行復雜的編程。新一代的數字放大器則可以自動檢測各種采樣速率和位深度,支持自動配置,無需任何編程。

在多通道的實現方案中,數字D類音頻放大器可以減少電路板上的外圍電容和布線。PCM輸入只需要BCLK、LRCLK和DIN三根連接線就可以輸出立體聲或8通道的TDM數據。而相比之下,模擬D類放大器一般需要兩個差分輸入信號共四根連接線,還需要額外的交流耦合電容(見圖1和圖2)。

大多數數字放大器同時需要較低的數字電源電壓(1.8V)和較高的揚聲器電源電壓(2.5V至5.5V)。但是使用MAX98357和MAX98360等單電源供電的D類放大器可以簡化電路設計并減少元件數量。MAX98365可以采用3.0V至5.5V的單電源供電,也可以采用1.8V至5.5V和3.0V至14.0V的雙電源供電。數字輸入的邏輯電平獨立于器件的電源電壓,輸入邏輯電平可以是1.2V至5.5V之間的任何值,無需邏輯電平轉換器。

抖動容差和時鐘發生

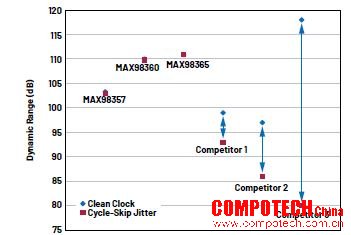

數字D類音頻放大器通常面臨時鐘抖動的新挑戰。為了獲得良好的音頻質量,大部分數字輸入放大器要求相當低的BCLK或MCLK的時鐘抖動。數據手冊通常不會具體給出抖動容差的數值,如果給出,典型值約為200ps的均方根抖動。較高的時鐘抖動通常會降低放大器的動態范圍或滿量程THD+N性能。

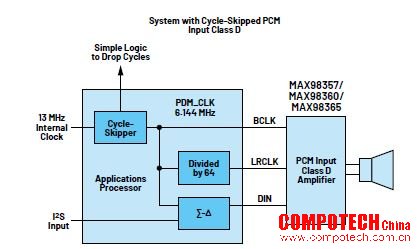

在許多系統中,處理器的基準振蕩器頻率不是BCLK的簡單倍數,因此為放大器提供低抖動的時鐘并不容易。例如,13MHz是GSM電話的常見晶振頻率、27MHz則通常用于視頻解決方案,這些基準頻率都不是44.1kSPS或48kSPS的音頻采樣速率的簡單倍數。因此,系統通常采用復雜的小數N分頻鎖相環來生成音頻專用的時鐘。在某些情況下,該解決方案需要單獨的音頻基準振蕩器,這會增加系統復雜性和物料成本。

另一種更好的解決方案是使用能容忍高時鐘抖動而不降低音頻性能的數字放大器。這種放大器可降低系統的復雜性。在最簡單的情況下,可以使用跳周期時鐘來產生BCLK,但這會產生異常高的抖動。如果跳過13MHz的基準時鐘周期產生6.144MHz的BCLK(48kSPS × 128OSR),則峰值抖動可達38.4ns,均方根抖動可達22.2ns(圖3),這比大多數DAC所能承受的抖動還要高出兩個數量級。

圖3.來自于25MHz時鐘跳周期生成的12.288MHz MCLK

然而,新型的D類音頻放大器即使在這樣的時鐘抖動下仍具備大于103dB的動態范圍性能。跳周期時鐘可通過處理器上的邏輯門電路來生成。新器件不需要鎖相環解決方案必需的振蕩器或環路濾波器。參見圖4。

圖4.小數N分頻鎖相環與跳周期時鐘實現

抖動容差測試結果

測試結果表明,使用跳周期時鐘時,MAX98357、MAX98360和MAX98365的動態范圍不會降低。此時,器件的動態范圍性能比120dB的DAC還高出20dB。Σ-Δ型DAC抖動容差的更多詳細數據可參見參考文章1。

圖5.動態范圍下降,跳周期時鐘抖動為11.5ns rms

結語

數字無濾波D類音頻放大器支持簡單的電路實現,無需額外的I2C編程、MCLK輸入、電平轉換器和EMI濾波器,具有高效率、低EMI和高輸出功率的特色。MAX98357和MAX98360采用WLP或QFN封裝,輸出功率可達3.2W。MAX98365采用WLP封裝,輸出功率可達17.6W。

參考資料

1Matt Felder, Patrick Gallagher, and Brian Donoghue. “Analyzing Audio DAC Jitter Sensitivity.” EDN Network, September, 2012.

關于ADI公司

Analog Devices, Inc. (NASDAQ: ADI)是全球領先的半導體公司,致力于在現實世界與數字世界之間架起橋梁,以實現智能邊緣領域的突破性創新。ADI提供結合模擬、數字和軟件技術的解決方案,推動數字化工廠、汽車和數字醫療等領域的持續發展,應對氣候變化挑戰,并建立人與世界萬物的可靠互聯。ADI公司2022財年收入超過120億美元,全球員工2.4萬余人。攜手全球12.5萬家客戶,ADI助力創新者不斷超越一切可能。更多信息,請訪問www.analog.com/cn。

關于作者

Matt Felder于2009年加入ADI公司,擔任模擬設計工程師。他的工作范圍包括音頻DAC、音頻ADC、多通道SAR ADC、音頻放大器、視頻DAC、FM無線電接收器和電池充電器。Matt是IEEE的高級會員,持有47項已發布的專利。他擁有德克薩斯農工大學的電氣工程學士學位和德克薩斯大學奧斯汀分校的電氣工程碩士學位。

本月熱點 HOME